# 82544El Gigabit Ethernet Controller

**Networking Silicon**

#### **Datasheet**

### **Product Features**

- Full IEEE 802.3ab compliant

- Auto-Negotiation of speed, duplex, and flow control configuration

- 32/64-bit 33/66 MHz, PCI Rev 2.2 compliant host interface

- Host interface compliant to the PCI-X addendum, revision 1.0a, from 50 MHz to 133 MHz

- Offers both hardware and software based IEEE 802.3z Auto-Negotiation and Link Setup for Ten-Bit Interface (TBI) mode

- Internally implements IEEE 802.3 MII management interface for monitoring and control of the internal PHY

- Offers an external link interface: TBI as specified in IEEE 802.3z standard for 1000 Mb/s full duplex operation with 1.25 Gb/s SERDES

- Receive and transmit IP and TCP/UDP checksum offloading capabilities

- Automatic MDI crossover operation for 100BASE-TX and 10BASE-T modes

- IEEE 802.1q VLAN support

- Implements enhanced ACPI register set and power down functionality supporting D0 and D3 states, Wake on LAN capability with Power Management Event support

- Provides adaptive Inter Frame Spacing (IFS) capability, enabling collision reduction in half duplex networks

- Enables control of the transmission of Pause packets through software or hardware triggering

- Provides indications of receive FIFO status through programming interface

- Provides six activity and link indication outputs to directly drive LEDs

- Provides external parallel interface for up to 4 Mb of Flash or Boot EPROM for boot agent capability

- 4-wire 64 x 16 serial EEPROM interface for loading product configuration information

- Operating temperature: 0°C to 70° C (ambient)

- Targeted power dissipation is 2.5 W maximum

- Provides boundary scan through IEEE 1149.1 (JTAG) Test Access Port

- Leaded and lead-free<sup>a</sup> 416-pin Ball Grid Array (BGA). Devices that are lead-free are marked with a circled "e1" and have a product code: NHXXXXX

a. This device is lead-free. That is, lead has not been intentionally added, but lead may still exist as an impurity at <1000 ppm. The Material Declaration Data Sheet, which includes lead impurity levels and the concentration of other Restriction on Hazardous Substances (RoHS) -banned materials, is available at:

$\verb|ftp://download.intel.com/design/packtech/material\_content_IC\_Pack| \\$

In addition, this device has been tested and conforms to the same parametric specifications as previous versions of the device. For more information regarding lead-free products from Intel Corporation, contact your Intel Field Sales representative.

# **Revision History**

| Revision | Revision Date | Description                             |

|----------|---------------|-----------------------------------------|

| 1.0      | April 2005    | Initial release (removed secret status) |

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82544El Gigabit Ethernet Controller described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2005

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Overv        | ew              |                                           | 1  |

|-----|--------------|-----------------|-------------------------------------------|----|

|     | 1.1          | Scope           |                                           | 1  |

|     | 1.2          | •               | ocuments                                  |    |

|     | 1.3          |                 | es                                        |    |

|     | 1.4          | Block Diagran   | n                                         | 3  |

| 2.0 | Additi       | nal Features of | f the 82544El Gigabit Ethernet Controller | 5  |

|     | 2.1          |                 | atures                                    |    |

|     | 2.2          | PHY-Specific    | Features                                  | 5  |

|     | 2.3          | Host Offloadir  | ng Features                               | 5  |

|     | 2.4          |                 | rformance Features                        |    |

|     | 2.5          |                 | vice Features                             |    |

|     | 2.6          | Technology F    | eatures                                   | 6  |

| 3.0 | Signa        | Descriptions    |                                           | 7  |

|     | 3.1          |                 | Definitions                               |    |

|     | 3.2          |                 | ıs Interface                              |    |

|     |              |                 | Address, Data and Control Signals         |    |

|     |              |                 | ration Signals                            |    |

|     |              |                 | upt Signal                                |    |

|     |              | •               | em Signals                                |    |

|     |              |                 | Reporting Signalser Management Signals    |    |

|     |              |                 | dance Compensation Signals                |    |

|     | 3.3          |                 | ace (TBI) Signals                         |    |

|     | 3.4          |                 | ASH Interface Signals                     |    |

|     | 3.5          |                 | s Signals                                 |    |

|     |              |                 | Signals                                   |    |

|     |              |                 | r Signals                                 |    |

|     | 3.6          | PHY Signals.    | -                                         | 15 |

|     |              | 3.6.1 Crysta    | al Signals                                | 15 |

|     |              |                 | og Signals                                |    |

|     | 3.7          |                 | e Signals                                 |    |

|     | 3.8          |                 | / Connections                             |    |

|     |              | •               | al Supplies                               |    |

|     |              |                 | og Supplies                               |    |

| 4.0 | <del>-</del> |                 | nd and No Connects                        |    |

| 4.0 | J            |                 | nd Timing Specifications                  |    |

|     | 4.1<br>4.2   | •               | olute Maximum Ratings                     |    |

|     | 4.2          |                 | ed Operating Conditions                   |    |

|     | 4.3<br>4.4   | •               | Characteristics                           |    |

|     | 4.5          | •               | ing Specifications                        |    |

|     | 7.0          |                 | PCI-X Bus Interface                       |    |

|     |              |                 | eted Link Interface Timing                |    |

|     |              | 0               | SH Interface                              |    |

|     |              |                 |                                           |    |

|                |       | 4.5.4 EEPROM Interface                                      | 31 |

|----------------|-------|-------------------------------------------------------------|----|

| 5.0            | Packa | age and Pinout Information                                  | 33 |

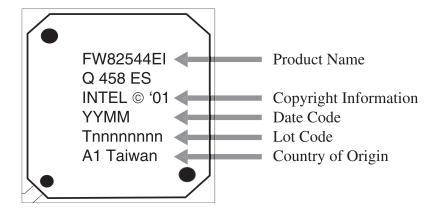

|                | 5.1   | Device Identification                                       | 33 |

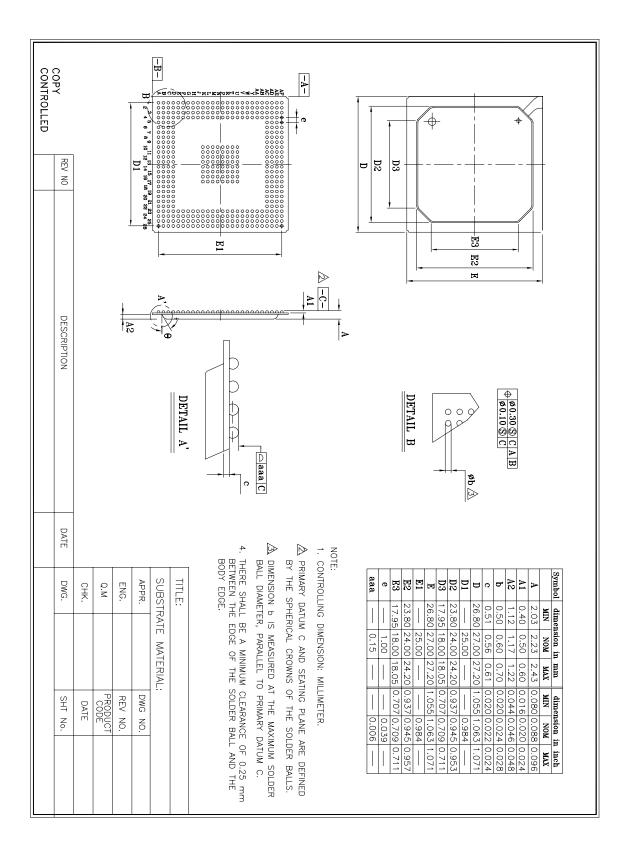

|                | 5.2   | Mechanical Specifications                                   | 33 |

|                | 5.3   | Targeted Thermal Specifications                             |    |

|                | 5.4   | Targeted Ball Mapping Diagram                               |    |

| <b>Figures</b> |       |                                                             |    |

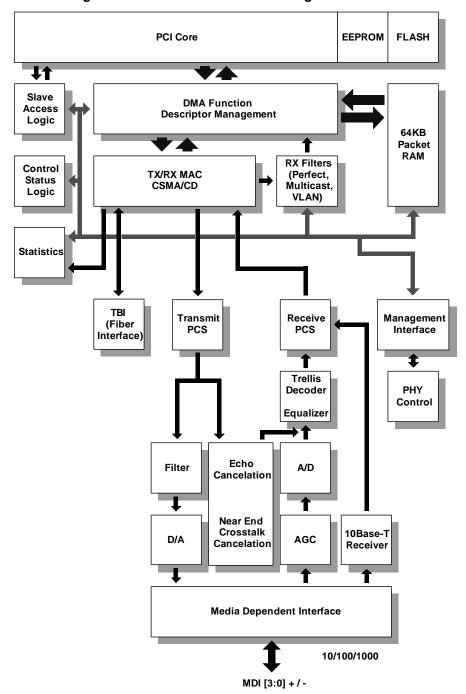

| O              | 1     | 82544EI Gigabit Ethernet Controller Block Diagram           | 3  |

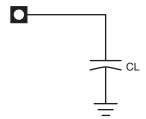

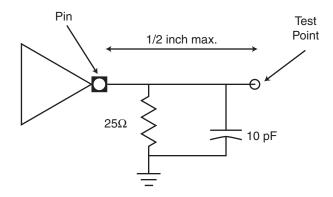

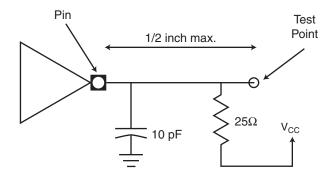

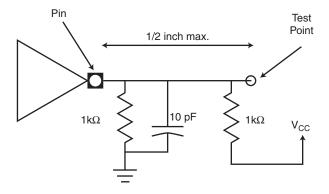

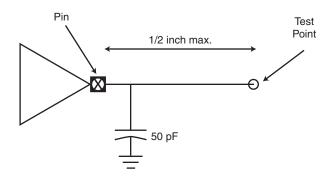

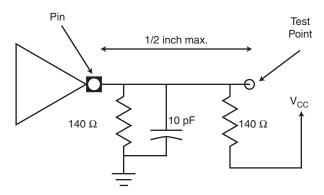

|                | 2     | AC Test Loads for General Output Pins                       | 22 |

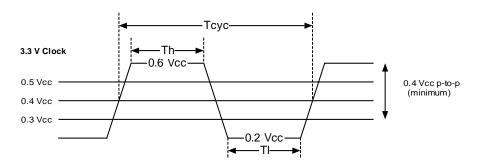

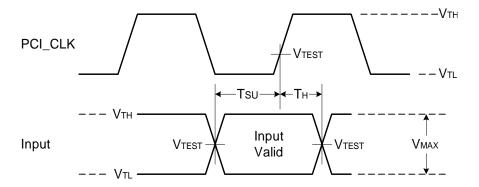

|                | 3     | PCI/PCI-X Clock Timing                                      | 23 |

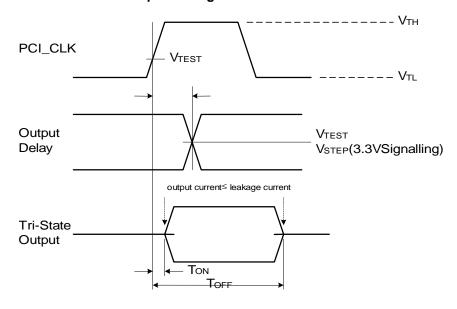

|                | 4     | PCI Bus Interface Output Timing Measurement Conditions      | 24 |

|                | 5     | PCI Bus Interface Input Timing Measurement Conditions       | 25 |

|                | 6     | TVAL (max) Rising Edge Test Load                            | 26 |

|                | 7     | TVAL (max) Falling Edge Test Load                           | 26 |

|                | 8     | TVAL (min) Test Load                                        | 26 |

|                | 9     | TVAL Test Load (PCI 5V Signalling Environment)              | 27 |

|                | 10    | Output Slew Rate Test Load (PCI-X only)                     | 27 |

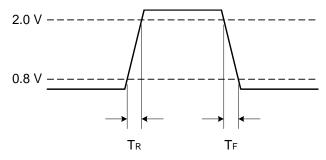

|                | 11    | Link Interface Rise/Fall Timing                             | 28 |

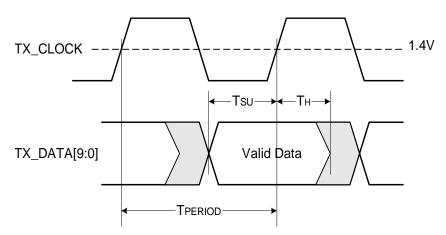

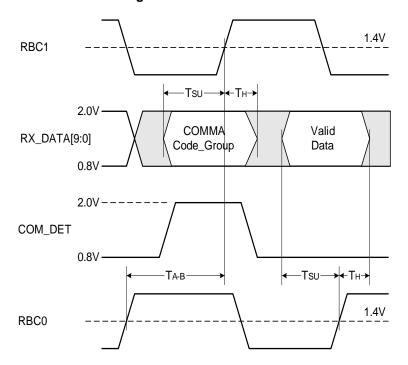

|                | 12    | Transmit Interface Timing                                   | 28 |

|                | 13    | Receive Interface Timing                                    |    |

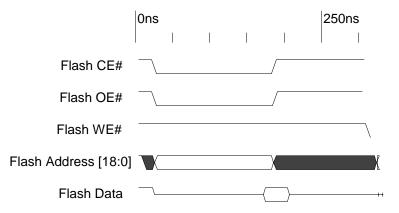

|                | 14    | Flash Read Timing                                           | 30 |

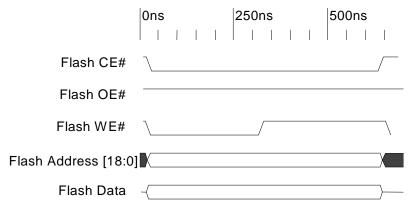

|                | 15    | Flash Write Timing                                          | 30 |

|                | 16    | Device Identification:                                      | 33 |

| Tables         |       |                                                             |    |

| Tables         |       |                                                             |    |

|                | 1     | Product Ordering Codes                                      |    |

|                | 1     | Absolute Maximum Ratings (Referenced to VSS [Ground])       |    |

|                | 2     | Recommended Operating Conditions                            |    |

|                | 3     | DC Specifications                                           |    |

|                | 4     | Power Supply Characteristics – 1                            |    |

|                | 5     | Power Supply Characteristics – 2                            |    |

|                | 6     | AC Characteristics: 3.3 V Interfacing                       |    |

|                | 7     | Switching Current                                           |    |

|                | 8     | 25Mhz Clock Input Requirements                              |    |

|                | 9     | Link Interface Clock Requirements                           | 21 |

|                | 10    | EEPROM Interface Clock Requirements                         |    |

|                | 11    | AC Test Loads for General Output Pins                       |    |

|                | 12    | PCI/PCI-X Bus Interface Clock Parameters                    |    |

|                | 13    | PCI/PCI-X BUS Interface Timing Parameters, ,                |    |

|                | 14    | PCI/PCI-X Bus Interface Timing Measurement Conditions       |    |

|                | 15    | Rise and Fall Time Definition                               | 27 |

|                | 16    | Transmit Interface Timing                                   | 28 |

|                | 17    | Receive Interface Receive Timing                            | 29 |

|                | 18    | Targeted Flash Read Operation Timing                        |    |

|                | 19    | Targeted Flash Write Operation Timing                       | 31 |

|                | 20    | EEPROM Interface Clock Timing                               | 31 |

|                | 21    | EEPROM Interface Clock Data Timing                          | 31 |

|                | 22    | 82544GC Gigabit Ethernet Controller Thermal Characteristics | 35 |

### 1.0 Overview

The 82544EI Gigabit Ethernet Controller is an integrated third-generation Ethernet LAN component capable of providing 1000, 100, and 10 Mbps data rates. It is a single-chip device, containing both the MAC and PHY layer functions, and optimized for LAN on Motherboard (LOM) designs, enterprise networking, and Internet appliances that use the Peripheral Component Interconnect (PCI) and PCI-X bus backplanes.

The 82544EI utilizes a 32/64 bit, 33/66 MHz direct interface to the PCI bus, compliant with the PCI Local Bus Specification, Revision 2.2. It also supports the emerging PCI-X extension to the PCI Local Bus, Revision 1.0a. The controller interfaces with the host processor through on-chip command and status registers and a shared host memory area, which is set up during initialization.

The 82544EI Gigabit Ethernet Controller provides a highly optimized architecture to deliver high performance and PCI/PCI-X bus efficiency. Its hardware, acceleration features enable offloading of various tasks, such as TCP/UDP/ IP checksum calculations and TCP segmentation, from the host processor. The 82544EI device accommodates highly-configurable Ethernet designs, which require minimal CPU overhead from interrupts and register accesses.

The physical layer circuitry provides an IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX and 10BASE-T applications. With the addition of an appropriate serializer/deserializer (SERDES), the 82544EI controller also provides an Ethernet interface for 1000BASE-SX or 1000BASE-LX applications.

The 82544EI Gigabit Ethernet Controller is packaged in a 27 mm x 27 mm, 416-ball grid array.

## 1.1 Scope

This document contains datasheet specifications for the 82544EI Gigabit Ethernet Controller including signal descriptions, DC and AC parameters, packaging data, and pinout information.

### 1.2 Reference Documents

This document assumes that the designer is acquainted with high-speed design and board layout techniques. The following documents provide additional information:

- 8254x Family of Gigabit Ethernet Controllers Software Developer's Manual, Intel Corporation.

- PCI Local Bus Specification, Revision 2.2, PCI Special Interest Group.

- PCI-X Specification, Revision 1.0a, PCI Special Interest Group.

- PCI Bus Power Management Interface Specification, Rev. 1.1, PCI Special Interest Group.

- IEEE Standard 802.3, 1996 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3u, 1995 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3x, 1997 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3z, 1998 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3ab, 1999 Edition, Institute of Electrical and Electronics Engineers (IEEE).

### 1.3 Product Codes

Table 1 lists the product ordering codes for the 82544EI.

**Table 1. Product Ordering Codes**

| Device              | Product Code |

|---------------------|--------------|

| 82544EI (Leaded)    | FW82544EI    |

| 82544EI (Lead Free) | NH82544EI    |

## 1.4 Block Diagram

Figure 1. 82544El Gigabit Ethernet Controller Block Diagram

*Note:* This page intentionally left blank.

# 2.0 Additional Features of the 82544El Gigabit Ethernet Controller

### 2.1 PCI/PCI-X Features

- Operates in either 5V or 3.3V PCI signaling environments

- 64-bit addressing for systems with more than 4 GB of physical memory

- Efficient PCI bus master operation, supported by optimized internal DMA controller

- Command usage optimization for advanced PCI commands such as MWI, MRM and MRL, and PCI-X commands such as MRD, MRB and MWB

## 2.2 PHY-Specific Features

- Complete full duplex and half duplex support

- Next page support

- Automatic polarity correction

- Digital implementation of adaptive equalizer and cancellers for echo and crosstalk

### 2.3 Host Offloading Features

- TCP segmentation (Large send)

- Packet filtering based on checksum errors

- Supports for various address filtering modes:

- 16 exact matches (unicast or multicast)

- 4096-bit hash filter for multicast frames

- Promiscuous unicast and promiscuous multicast transfer modes

- IEEE 802.1q VLAN support

- Ability to add and strip IEEE 802.1q VLAN tags

- Packet filtering based on VLAN tagging, supporting 4096 tags

- SNMP and RMON statistic counters

### 2.4 Additional Performance Features

- Programmable host memory receive buffers (256 B to 16 KB)

- Programmable cache line size from 16 B to 128 B for efficient usage of PCI bandwidth

- Implements a total of 64 KB of configurable receive and transmit data FIFOs:

- default allocation is 48 KB for Receive data FIFO and 16 KB for transmit data FIFO

- Descriptor ring management hardware for transmit and receive:

- optimized descriptor fetching and write-back mechanisms for efficient system memory and PCI bandwidth usage

- Provides a mechanism for reducing the number of interrupts generated by receive and transmit operations

- Supports reception and transmission of packets with length up to 16 KB

### 2.5 Additional Device Features

- Provides seven general-purpose user mode pins

- Supports little-endian byte ordering for both 32- and 64-bit systems

- Supports big-endian byte ordering for 64-bit systems

- Provides loopback capabilities

- Provides boundary scan through IEEE 1149.1 (JTAG) Test Access Port

## 2.6 Technology Features

- Implemented in 0.18µ process

- Packaged in 416 PBGA package (27 mm x 27 mm)

- Implemented as low power CMOS device

## 3.0 Signal Descriptions

**Special Note:** The targeted signal names are subject to change without notice. Verify with your local Intel sales office that you have the latest data sheet before finalizing a design.

## 3.1 Signal Type Definitions

The signals of the 82544EI controller are electrically defined in the following fashion:

| Name | Definition                                                                                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | A standard input-only digital signal.                                                                                                                                                                                                                                                                                      |

| 0    | A standard output-only digital signal.                                                                                                                                                                                                                                                                                     |

| TS   | A bi-directional, three-state digital input/output signal.                                                                                                                                                                                                                                                                 |

| STS  | A sustained, digital, three-state signal that is driven by one owner at a time. An agent that drives an STS pin low must actively drive it high for at least one clock before letting it float. The next owner of the signal cannot start driving it any sooner than one clock after it is released by the previous owner. |

| OD   | An open-drain digital signal. It is wired-OR'ed with other agents. The signaling agent asserts the signal, but the signal is returned to the inactive state by a weak pull-up resistor. The pull-up resistor may take two or three clock periods to fully restore the signal to the deasserted state.                      |

| Α    | PHY analog data signal.                                                                                                                                                                                                                                                                                                    |

| Р    | A power connection, voltage reference, or other reference connection.                                                                                                                                                                                                                                                      |

### 3.2 PCI/PCI-X Bus Interface

When RST# is asserted, the 82544EI Gigabit Ethernet Controller will not drive any PCI output or bi-directional pins except PME#.

## 3.2.1 PCI Address, Data and Control Signals

| Signal Name | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[63:0]    | TS   | Address and Data. Address and Data are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases.                                                                                                                                                                                                                                         |

|             |      | The address phase is the clock cycle in which FRAME# is asserted. During the address phase AD[63:0] contain a physical address (64 bits). For I/O, this is a byte address; for configuration and memory, it is a DWORD address. The 82544EI device uses little endian byte ordering.                                                                                                                 |

|             |      | During data phases AD[7:0] contain the least significant byte (LSB) and AD[63:56] contain the most significant byte (MSB).                                                                                                                                                                                                                                                                           |

|             |      | The 82544EI controller may be optionally connected to a 32-bit PCI Local Bus. On a 32-bit bus, AD[63:32] and other signals corresponding to the high order byte lanes do not participate in the bus cycle.                                                                                                                                                                                           |

| CBE[7:0]#   | TS   | <b>Bus Command and Byte Enables.</b> Bus Command and Byte Enables are multiplexed on the same PCI pins.                                                                                                                                                                                                                                                                                              |

|             |      | During the address phase of a transaction, CBE#[7:0] define the bus command. During the data phase CBE#[7:0] are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data.                                                                                                                                                    |

|             |      | CBE#[0] applies to byte 0 (LSB) and CBE#[7] applies to byte 7 (MSB).                                                                                                                                                                                                                                                                                                                                 |

| PAR         | TS   | Parity. Parity issued to implement Even Parity across AD[31:0] and CBE#[3:0]. PAR is stable and valid one clock after the address phase. For data phases, PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted after a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase. |

|             |      | When the 82544EI controller is a bus master, it drives PAR for address and write data phases. As a slave, it drives PAR for read data phases.                                                                                                                                                                                                                                                        |

| PAR64       | TS   | Parity 64. Parity issued to implement Even Parity across AD[63:32] and CBE#[7:4]. PAR64 is stable and valid one clock after the address phase.                                                                                                                                                                                                                                                       |

|             |      | For data phases, PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted after a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase.                                                                                                                                          |

|             |      | When the 82544El controller is a bus master, it drives PAR64 for address and write data phases. As a slave, it drives PAR64 for read data phases.                                                                                                                                                                                                                                                    |

| FRAME#      | STS  | <b>FRAME.</b> FRAME# is driven by the 82544EI device to indicate the beginning and duration of an access. FRAME# is asserted to indicate the beginning of a bus transaction.                                                                                                                                                                                                                         |

|             |      | While FRAME# is asserted, data transfers continue. When FRAME# is asserted, the transaction is in the final data phase.                                                                                                                                                                                                                                                                              |

| IRDY#       | STS  | Initiator Ready. IRDY# indicates the ability of the 82544EI controller (as a bus master device) to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#.                                                                                                                                                                                                      |

|             |      | A data phase is completed on any clock in which both IRDY# and TRDY# are sampled asserted.                                                                                                                                                                                                                                                                                                           |

|             |      | During a write, IRDY# indicates that valid data is present on AD[63:0]. During a read, it indicates the master is ready to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82544El controller drives IRDY# when acting as a master and samples it when acting as a slave.                                                                                |

| Signal Name | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRDY#       | STS  | Target Ready. TRDY# indicates the ability of the 82544EI controller (as a selected device) to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#.                                                                                                                                                                                                                   |

|             |      | A data phase is completed on any clock in which both TRDY# and IRDY# are sampled asserted. During a read, TRDY# indicates that valid data is present on AD[63:0]. During a write, it indicates the target is ready to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82544El device drives IRDY# when acting as a slave and samples it when acting as a master. |

| STOP#       | STS  | <b>Stop.</b> STOP# indicates the current target is requesting the master to stop the current transaction. As a slave, the 82544EI controller drives STOP# to request the bus master to stop the transaction. As a master, the 82544EI controller receives STOP# from the slave and stops the current transaction.                                                                                            |

| IDSEL       | I    | Initialization Device Select. IDSEL is used by the 82544El device as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                         |

| DEVSEL#     | STS  | <b>Device Select.</b> When being actively driven by the 82544El controller, DEVSEL# indicates to the bus master that it has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.                                                                                                                                         |

| VIO         | Р    | <b>VIO.</b> VIO is a voltage reference for PCI interface (3.3 V or 5 V). It is used as the clamping voltage.                                                                                                                                                                                                                                                                                                 |

|             |      | NOTE: An external resistor is required between the voltage reference and the VIO balls. The targeted resistor value is 100 K $\Omega$ .                                                                                                                                                                                                                                                                      |

## 3.2.2 Arbitration Signals

| Signal Name | Туре | Name and Function                                                                                                                                                                             |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ64#      | TS   | Request Transfer. REQ64# is generated by the current initiator to indicate its desire to perform a 64-bit transfer. REQ64# has the same timing as the FRAME# signal.                          |

| ACK64#      | TS   | <b>Acknowledge Transfer.</b> ACK64# is generated by the currently-addressed target in response to a REQ64# assertion by the initiator. ACK64# has the same timing as the DEVSEL# signal.      |

| REQ#        | TS   | Request Bus. REQ# indicates to the arbiter that the 82544EI controller desires use of the bus. This is a point to point signal.                                                               |

| GNT#        | I    | <b>Grant Bus.</b> GNT# indicates to the 82544EI device that access to the bus has been granted. This is a point to point signal                                                               |

| LOCK#       | I    | <b>Lock Bus.</b> LOCK# is asserted by an initiator to require sole access to a target memory device during two or more separate transfers. The 82544EI device does not implement bus locking. |

## 3.2.3 Interrupt Signal

| Signal Name | Туре | Name and Function                                                                                                                           |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| INTA#       |      | Interrupt A. The signal is used to request an interrupt by the 82544El controller. This is an active low, level-triggered interrupt signal. |

## 3.2.4 System Signals

| Signal Name | Туре | Name and Function                                                                                                                                                                                                                                                                            |

|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         | I    | PCI_Clock. CLK provides timing for all transactions on the PCI bus and is an input to the 82544El device. All other PCI signals, except RST# and INTA# lines are sampled on the rising edge of CLK. All other timing parameters are defined with respect to this edge.                       |

| M66EN       | I    | <b>66 MHz Enable.</b> M66EN indicates whether the system bus is enabled for 66MHz if the slot is capable of that operating frequency. This signal is ignored by the 82544El controller, but should be connected properly for future compatibility.                                           |

| RST#        | I    | PCI Reset. Most of the internal state of the 82544EI controller is reset on the de-assertion (rising edge) of RST#. Whenever RST# is asserted, all PCI output signals except PME# are floated and inputs are ignored. The PME# context is preserved, depending on power management settings. |

## 3.2.5 Error Reporting Signals

| Signal Name | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERR#       | OD   | <b>System Error.</b> SERR# is used by the 82544EI controller to report address parity errors. SERR# is open drain and is actively driven for a single PCI clock when reporting the error.                                                                                                                                                                                                                        |

| PERR#       | STS  | Parity Error. PERR# is used by the 82544EI controller to report data parity errors during all PCI transactions except by a Special Cycle. PERR# is sustained tri-state and must be driven active by the 82544EI controller receive data two clocks following the data when a data parity error is detected. The minimum duration of PERR# is one clock for each data phase that a data parity error is detected. |

### 3.2.6 Power Management Signals

| Signal Name    | Туре | Name and Function                                                                                                                                                                                                                                                                         |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN_PWR_GOOD   | I    | Power Good (Power-On Reset). The LAN_PWR_GOOD signal indicates that good power is available for 82544EI device. When the signal is zero, the 82544EI controller will hold the entire chip in reset state and float all PCI signals.                                                       |

| PME#           | OD   | Power Management Event. The 82544EI device will drive this signal to zero when it receives a wakeup event and either the PME_En bit in the Power Management Control / Status Register is 1 or the Advanced Power Management Enable (APME) bit of the Wake Up Control Register (WUC) is 1. |

| APM_WAKEUP     | 0    | Advance Power Management Wakeup. When APM Wakeup is enabled in the 82544EI controller and the 82544EI controller receives a Magic Packet* it will set this signal to a logic 1 for 50 ms.                                                                                                 |

| AUX_PWR        | I    | <b>Auxiliary Power Available.</b> If AUX_PWR equals 1, it indicates that Auxiliary Power is available and the 82544EI device should support D3 <sub>cold</sub> power state.                                                                                                               |

| PWR_STATE[1:0] | 0    | Power State. The bits are set in the following power states:                                                                                                                                                                                                                              |

|                |      | 00b = D0u, D1, or D3 state with wakeup disabled                                                                                                                                                                                                                                           |

|                |      | No PHY operation is required                                                                                                                                                                                                                                                              |

|                |      | 01b = D0u, D1, or D3 state with wakeup enabled                                                                                                                                                                                                                                            |

|                |      | <ul> <li>PHY operation is required in this state, although it may be at low<br/>speed.</li> </ul>                                                                                                                                                                                         |

|                |      | 11b = D0 active state                                                                                                                                                                                                                                                                     |

|                |      | Full speed PHY operation is required.                                                                                                                                                                                                                                                     |

|                |      | The resulting meaning of the bits is as follows:                                                                                                                                                                                                                                          |

|                |      | Bit 1: asserted when normal (full power/speed) operation is required.                                                                                                                                                                                                                     |

|                |      | Bit 0: asserted when link is required.                                                                                                                                                                                                                                                    |

|                |      | The polarity of bit 0 and 1 may be individually inverted by setting the IPS0 and IPS1 bits in the Extended Device Control Register (CTRL_EXT), respectively.                                                                                                                              |

### 3.2.7 Impedance Compensation Signals

| Signal Name | Туре | Name and Function                                                                                                                                                                                                                                                  |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZN_COMP     | I/O  | N Device Impedance Compensation. Connect to an external precision resistor (to VDD) that is indicative of the PCI/PCI-X trace load. This cell is used to dynamically determine the drive strength required on the N-channel transistors in the PCI/PCI-X IO cells. |

| ZP_COMP     | I/O  | P Device Impedance Compensation. Connect to an external precision resistor (to VSS) that is indicative of the PCI/PCI-X trace load. This cell is used to dynamically determine the drive strength required on the P-channel transistors in the PCI/PCI-X IO cells. |

## 3.3 Ten-Bit Interface (TBI) Signals

The TBI is a MAC interface that can connect to an external Serializer/Deserializer (SERDES) device for fiber-based designs. When the 82544EI controller is not in TBI mode, the TBI signals are in a high-impedance state.

The 82544EI device has a special GMII test mode for the IEEE Unfiltered Jitter Test. This test mode reuses the TBI signals as GMII outputs. After PHY conformance testing is completed, it is permissible to gang the TBI interface pins together to reduce the number of pulldown resistors needed.

| Signal Name  | Туре | Name and Function                                                                                                                                                                                                                                          |  |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TBI_MODE     | I    | <b>TBI Mode Enable.</b> This signal forces the device into TBI mode when TBI_MODE is asserted (high).                                                                                                                                                      |  |

| TX_DATA[9:0] | 0    | <b>Transmit Data.</b> Parallel TBI data bus to be transmitted through a serializer/deserializer (SERDES). If TBI mode is not used, connect these pins to ground through pulldown resistors. During GMII test mode these pins become GMII outputs.          |  |

| GTX_CLK      | 0    | <b>Transmit Clock.</b> Operates at 125 MHz. If TBI mode is not used, connect this ball to ground through a pulldown resistor. During GMII test mode this pin becomes the transmit clock test output.                                                       |  |

| EWRAP        | 0    | <b>Enable Wrap.</b> EWRAP is low in normal operation. When it is high, the SERDES device is forced to transceiver loopback the serialized transmit data to the receiver. If TBI mode is not used, connect this ball to ground through a pulldown resistor. |  |

| RX_DATA[9:0] | I    | Receive Data. Parallel TBI data bus received from a serializer/ deserializer (SERDES). If TBI mode is not used, connect these balls to ground through a pulldown resistor. During GMII test mode these pins become GMII outputs.                           |  |

| RBC0         | I    | <b>Receive Clock.</b> RBC0 is the 62.5 MHz receive clock. If TBI mode is not used, connect this ball to ground through a pulldown resistor. During GMII test mode this pin becomes an output.                                                              |  |

| RBC1         | I    | Receive Clock: RBC1 is the 62.5 MHz receive clock shifted 180 degrees from RBC0. If TBI mode is not used, connect this ball to ground through a pulldown resistor. During GMII test mode this pin becomes the receive clock test output.                   |  |

# 3.4 EEPROM/FLASH Interface Signals

| Signal Name   | Туре | Name and Function                                                                                          |

|---------------|------|------------------------------------------------------------------------------------------------------------|

| EE_DI         | 0    | EEPROM DI. This pin is an output to the memory device.                                                     |

| EE_DO         | I    | <b>EEPROM DO.</b> This pin is an input from the memory device. Internal pullup resistor provided.          |

| EE_CS         | 0    | EEPROM CSO. Used to enable the device.                                                                     |

| EE_SK         | 0    | <b>EEPROM Serial Clock.</b> The clock rate of the EEPROM interface is approximately 1 MHz.                 |

| FL_ADDR[18:0] | 0    | FLASH Address Outputs. Used to FLASH or Boot ROM                                                           |

| FL_CS#        | 0    | FLASH Chip Select. Used to enable FLASH or Boot ROM                                                        |

| FL_OE#        | 0    | FLASH Output Enable. Used to enable buffers in FLASH.                                                      |

| FL_WE#        | 0    | FLASH Write Enable Output. Used for write cycles.                                                          |

| FL_DATA[7:0]  | TS   | <b>FLASH Data I/O.</b> Bi-directional data bus for FLASH data. These signals have internal pullup devices. |

## 3.5 Miscellaneous Signals

## 3.5.1 LED Signals

| Signal Name  | Туре | Name and Function                                                                                                                                         |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINK_UP#     | 0    | Link Up. LINK_UP# indicates link connectivity                                                                                                             |

| RX_ACTIVITY# | OD   | Receive Activity. Flashes an LED to indicate link receive activity. This output uses an open drain cell to allow a wired-OR of activity signals.          |

| TX_ACTIVITY# | OD   | <b>Transmit Activity.</b> Flashes an LED to indicate link transmit activity. This output uses an open drain cell to allow a wired-OR of activity signals. |

| LINK10#      | OD   | <b>Link 10.</b> Drives an LED to indicate link at 10 Mbps. This output uses an open drain cell.                                                           |

| LINK100#     | OD   | Link 100. Drives an LED to indicate link at 100 Mbps. This output uses an open drain cell.                                                                |

| LINK1000#    | OD   | <b>Link 1000.</b> Drives an LED to indicate link at 1000 Mbps. This output uses an open drain cell.                                                       |

## 3.5.2 Other Signals

| Signal Name | Туре | Name and Function                                                                                  |

|-------------|------|----------------------------------------------------------------------------------------------------|

| LOS         | I    | Loss of Signal. Loss of signal from the optical transceiver when TBI_MODE=1                        |

| XOFF        | I    | <b>External XOFF.</b> This is an external indication of the Above High Threshold for flow control. |

| XON         | I    | <b>External XON.</b> This provides an external indication of Below Low Threshold for flow control. |

| Signal Name          | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABV_HI               | 0    | <b>Above High Threshold.</b> Output indicating the RX FIFO fullness is above the programmed high threshold.                                                                                                                                                                                                                                                                                                                  |

| BLW_LO               | 0    | <b>Below Low Threshold.</b> Output indicating the RX FIFO fullness is below the programmed low threshold.                                                                                                                                                                                                                                                                                                                    |

| SDP[7:6]<br>SDP[4:0] | TS   | S/W Defined Pins. These pins are reserved pins which are software programmable with respect to input/output capability. These default to inputs upon power up but may have their direction and output values defined in the EEPROM. The upper four bits may be mapped to the General Purpose Interrupt bits when configured as inputs.  SPECIAL NOTE: SDP5 is intentionally missing from the group of software-defined pins. |

| TEST0                | I    | Factory Test Pin. Connect this ball to ground through a pulldown resistor.                                                                                                                                                                                                                                                                                                                                                   |

| TEST1                |      | Factory Test Pin. Attach an external pullup resistor to the pin to ensure the test mode is disabled. Use a common value resistor such as 1 K $\Omega$ (the value is not critical). Alternatively, the pin may be connected directory to the 3.3V supply.                                                                                                                                                                     |

| GMII_TEST[1:0]       | I    | GMII Test Mode Pins. For normal operation, the test pins are connected to ground through a common pulldown resistor. For PHY Unfiltered Jitter Test, drive both pins high.                                                                                                                                                                                                                                                   |

| COL_TEST             | 0    | <b>Collision Test Pin.</b> For normal operation, these pins are connected to ground through a pulldown resistor. During GMII test mode it is driving as an output.                                                                                                                                                                                                                                                           |

| CRS_TEST             | 0    | Carrier Sense Test Pin. For normal operation, this pin is connected to ground through a pulldown resistor. It is driven as an output during GMII test mode.                                                                                                                                                                                                                                                                  |

# 3.6 PHY Signals

## 3.6.1 Crystal Signals

| Signal Name | Туре | Name and Function                                                                                                                                   |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1       | I    | XTAL1. 25MHz +/- 30 ppm input; can be connected to an oscillator or a crystal. If a crystal is used, XTAL2 must be connected as well.               |

| XTAL2       | 0    | XTAL2. Output of internal oscillator circuit used to drive crystal into oscillation. If an external oscillator is used, XTAL2 must be disconnected. |

## 3.6.2 Analog Signals

| Signal Name | Туре |                | Name and Function                                                                                                               |

|-------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------|

| REF         | Р    | Reference. Ext | ernal 2.49 K $\Omega$ resistor connection to VSS.                                                                               |

| MDI[0]+/-   | Α    | Media Depend   | ent Interface[0].                                                                                                               |

|             |      | 1000BASE-T:    | In MDI configuration, MDI[0]+/- corresponds to BI_DA+/- and in MDIX configuration MDI[0]+/- corresponds to BI_DB+/              |

|             |      | 100BASE-TX:    | In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for the receive pair. |

|             |      | 10BASE-T:      | In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for the receive pair. |

| MDI[1]+/-   | Α    | Media Depend   | ent Interface[1].                                                                                                               |

|             |      | 1000BASE-T:    | In MDI configuration, MDI[1]+/- corresponds to BI_DB+/-, and in MDIX configuration, to the BI_DA+/                              |

|             |      | 100BASE-TX:    | In MDI configuration, MDI[1]+/- is used for the receive pair, and in MDIX configuration, the transmit pair.                     |

|             |      | 10BASE-T:      | In MDI configuration, MDI[1]+/- is used for the receive pair, and in MDIX configuration, the transmit pair.                     |

| MDI[2]+/-   | Α    | Media Depend   | ent Interface[2].                                                                                                               |

|             |      | 1000BASE-T:    | In MDI configuration, MDI[2]+/- corresponds to BI_DC+/-, and in MDIX configuration, to the BI_DD+/                              |

|             |      | 100BASE-TX:    | Unused.                                                                                                                         |

|             |      | 10BASE-T:      | Unused.                                                                                                                         |

| MDI[3]+/-   | Α    | Media Depend   | ent Interface[3].                                                                                                               |

|             |      | 1000BASE-T:    | In MDI configuration, MDI[3]+/- corresponds to BI_DD+/-, and in MDIX configuration, to the BI_DC+/                              |

|             |      | 100BASE-TX:    | Unused.                                                                                                                         |

|             |      | 10BASE-T:      | Unused.                                                                                                                         |

## 3.7 Test Interface Signals

| Signal Name | Туре | Name and Function                                                                                                    |

|-------------|------|----------------------------------------------------------------------------------------------------------------------|

| JTAG_TCK    | I    | JTAG Clock. Input to device                                                                                          |

| JTAG_TDI    | I    | JTAG TDI. Input to device                                                                                            |

| JTAG_TDO    | 0    | JTAG TDO. Output from device                                                                                         |

| JTAG_TMS    | I    | JTAG TMS. Input to device                                                                                            |

| JTAG_TRST#  | I    | JTAG Reset. Active low reset for JTAG. Terminate this signal through a resistor to ground. Do not leave unconnected. |

## 3.8 Power Supply Connections

## 3.8.1 Digital Supplies

| Signal Name | Туре | Name and Function                              |

|-------------|------|------------------------------------------------|

| VDDO        | Р    | VDDO. 3.3 V I/O power supply.                  |

| DVDDH       | Р    | <b>DVDDH.</b> 1.8 V Digital core power supply. |

| DVDDL       | Р    | <b>DVDDL.</b> 1.5 V Digital core power supply. |

### 3.8.2 Analog Supplies

| Signal Name | Туре | Name and Function                 |

|-------------|------|-----------------------------------|

| AVDDH       | Р    | AVDDH. 3.3 V Analog power supply. |

| AVDDL       | Р    | AVDDL. 2.5 V Analog power supply. |

### 3.8.3 Ground and No Connects

| Signal Name | Туре | Name and Function                                                                                         |

|-------------|------|-----------------------------------------------------------------------------------------------------------|

| GND         | Р    | Grounds.                                                                                                  |

| NO_CONNECT  | Р    | <b>No Connects.</b> Do not connect to these pins to any circuit. Do not use pullup or pulldown resistors. |

#### **Targeted Electrical and Timing Specifications** 4.0

#### 4.1 **Targeted Absolute Maximum Ratings**

Table 1. Absolute Maximum Ratings (Referenced to VSS [Ground])<sup>a</sup>

| Symbol               | Parameter                                                                                               | Min       | Max                                                                         | Units |

|----------------------|---------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------|-------|

| V <sub>DD(3.3)</sub> | DC supply voltage on VDDD or AVDDH with respect to VSS                                                  | VSS - 0.5 | 4.6                                                                         | V     |

| V <sub>DD(2.5)</sub> | DC supply voltage on AVDDL with respect to VSS                                                          | VSS - 0.5 | 4.6 or<br>V <sub>DD(2.5)</sub> + 0.5<br>(whichever is<br>less) <sup>b</sup> | V     |

| V <sub>DD(1.8)</sub> | DC supply voltage on DVDDH with respect to VSS                                                          | VSS - 0.5 | 4.6 or<br>V <sub>DD(2.5)</sub> + 0.5<br>(whichever is<br>less) <sup>b</sup> | V     |

| V <sub>DD(1.5)</sub> | DC supply voltage on DVDDL with respect to VSS                                                          | VSS - 0.5 | 4.6 or<br>V <sub>DD(2.5)</sub> + 0.5<br>(whichever is<br>less) <sup>b</sup> | V     |

| $V_{DD}$             | DC supply voltage                                                                                       | VSS - 0.5 | 4.6                                                                         | V     |

| VI / VO              | LVTTL input voltage                                                                                     | VSS - 0.5 | 4.6                                                                         | V     |

| VI / VO              | 5 V compatible input voltage                                                                            | VSS - 0.5 | 6.6                                                                         | V     |

| Io                   | DC output current (by cell type):                                                                       |           |                                                                             | mA    |

|                      | I <sub>OL = 1mA</sub>                                                                                   |           | 3                                                                           |       |

|                      | $I_{OL=2 \text{ mA}}$                                                                                   |           | 7                                                                           |       |

|                      | I <sub>OL</sub> = 3 mA                                                                                  |           | 10                                                                          |       |

|                      | I <sub>OL</sub> = 6 mA                                                                                  |           | 20                                                                          |       |

|                      | I <sub>OL</sub> = 9 mA                                                                                  |           | 30                                                                          |       |

|                      | I <sub>OL</sub> = 12 mA                                                                                 |           | 40                                                                          |       |

|                      | I <sub>OL</sub> = 18 mA                                                                                 |           | 60                                                                          |       |

|                      | I <sub>OL</sub> = 24 mA                                                                                 |           | 75                                                                          |       |

| $T_{STG}$            | Storage temperature range                                                                               | -40       | 125                                                                         | °C    |

|                      | ESD per MIL_STD-883 Test Method 3015,<br>Specification 2001V Latchup Over/Undershoot:<br>±150 mA, 125 C |           | V <sub>DD</sub><br>overstress:<br>V <sub>DD(3.3)</sub> (7.2 V)              | V     |

Permanent device damage is likely to occur if the ratings in this table are exceeded. These values should not be used as

the limits for normal device operations.

This specification applies to biasing the device to a steady state for an indefinite duration. During normal device powerup, explicit power sequencing is not required.

## 4.2 Recommended Operating Conditions

Table 2. Recommended Operating Conditions<sup>a</sup>

| Symbol                                                              | Parameter                                       | Min  | Max  | Units |

|---------------------------------------------------------------------|-------------------------------------------------|------|------|-------|

| V <sub>DD(3.3)</sub>                                                | DC supply voltage on VDDD or AVDDH <sup>b</sup> | 3.0  | 3.6  | V     |

| V <sub>DD(2.5)</sub> DC supply voltage on AVDDL <sup>c</sup>        |                                                 | 2.38 | 2.62 | V     |

| V <sub>DD(1.8)</sub> DC supply voltage on DVDDH <sup>c</sup>        |                                                 | 1.71 | 1.89 | V     |

| V <sub>DD(1.5)</sub> DC supply voltage on DVDDL <sup>c</sup>        |                                                 | 1.43 | 1.57 | V     |

| VIO                                                                 | PCI bus voltage reference                       | 3.0  | 5.25 | V     |

| t <sub>R</sub> /t <sub>F</sub>                                      | Input rise/fall time (normal input)             | 0    | 200  | ns    |

| t <sub>r</sub> /t <sub>f</sub> Input rise/fall time (Schmitt input) |                                                 | 0    | 10   | ms    |

| T <sub>A</sub> Operating temperature range (ambient)                |                                                 | 0    | 70   | С     |

| T <sub>J</sub>                                                      | T <sub>J</sub> Junction temperature             |      | ≤125 | С     |

a. For normal device operations, adhere to the limits in this table. Sustained operation of a device at conditions exceeding these values, even if they are within the absolute maximum rating limits, might result in permanent guaranteed if conditions exceed recommended operating conditions.

## 4.3 Targeted DC Specifications

Table 3. DC Specifications

| Symbol               | Parameter                          | Condition | Min  | Тур | Max  | Units |

|----------------------|------------------------------------|-----------|------|-----|------|-------|

| V <sub>DD(3.3)</sub> | DC supply voltage on VDDO or AVDDH |           | 3.00 | 3.3 | 3.60 | V     |

| V <sub>DD(2.5)</sub> | DC supply voltage on AVDDL         |           | 2.38 | 2.5 | 2.62 | V     |

| V <sub>DD(1.8)</sub> | DC supply voltage on DVDDH         |           | 1.71 | 1.8 | 1.89 | V     |

| V <sub>DD(1.5)</sub> | DC supply voltage on DVDDL         |           | 1.43 | 1.5 | 1.57 | V     |

Table 4. Power Supply Characteristics – 1 (Sheet 1 of 2)

| Symbol               | Parameter            | Condition              | Min | Typ <sup>a</sup> | Max <sup>b</sup> | Units |

|----------------------|----------------------|------------------------|-----|------------------|------------------|-------|

| I <sub>CC(3.3)</sub> | 3.3 V supply current | TBI mode               |     | 200              | 230              | mA    |

|                      |                      | 1000BASE-T             |     | 130              | 160              |       |

|                      |                      | 100BASE-T              |     | 90               | 110              |       |

|                      |                      | 10BASE-T               |     | 85               | 105              |       |

|                      |                      | Powerdown <sup>c</sup> |     | 85               | 105              |       |

|                      |                      | Quiescent <sup>d</sup> |     | 50               | 60               |       |

b. It is recommended that  $\dot{V}DD0 = AVDDH$  during powerup and normal operation.

c. It is recommended that both VDDO and AVVDH are greater than AVDDL > DVDDH > DVDDL during powerup. However, voltage sequencing is not a strict requirement as long as the power supply ramp is faster than approximately 200 ms.

Table 4. Power Supply Characteristics – 1 (Sheet 2 of 2) (Continued)

| Symbol               | Parameter            | Condition              | Min | Typ <sup>a</sup> | Max <sup>b</sup> | Units |

|----------------------|----------------------|------------------------|-----|------------------|------------------|-------|

| I <sub>CC(2.5)</sub> | 2.5 V supply current | TBI mode               |     | 2.2              | 2.6              | mA    |

|                      |                      | 1000BASE-T             |     | 340              | 410              |       |

|                      |                      | 100BASE-T              |     | 85               | 105              |       |

|                      |                      | 10BASE-T               |     | 125              | 150              |       |

|                      |                      | Powerdown <sup>c</sup> |     | 85               | 105              |       |

|                      |                      | Quiescent <sup>d</sup> |     | 2.0              | 2.5              |       |

| I <sub>CC(1.8)</sub> | 1.8 V supply current | TBI mode               |     | 170              | 200              | mA    |

|                      |                      | 1000BASE-T             |     | 300              | 360              |       |

|                      |                      | 100BASE-T              |     | 160              | 200              |       |

|                      |                      | 10BASE-T               |     | 110              | 135              |       |

|                      |                      | Powerdown <sup>c</sup> |     | 90               | 110              |       |

|                      |                      | Quiescent <sup>d</sup> |     | 15               | 20               |       |

| I <sub>CC(1.5)</sub> | 1.5 V supply current | TBI mode               |     | 0.4              | 0.5              | mA    |

|                      |                      | 1000BASE-T             |     | 200              | 240              |       |

|                      |                      | 100BASE-T              |     | 0.3              | 0.4              |       |

|                      |                      | 10BASE-T               |     | 0.2              | 0.3              |       |

|                      |                      | Powerdown <sup>c</sup> |     | 0.1              | 0.15             |       |

|                      |                      | Quiescent <sup>d</sup> |     | 0.1              | 0.15             |       |

Typical conditions are T<sub>A</sub> = 25 C, voltages are nominal. Where applicable, network traffic is moderate at full duplex and the system interface is PCI 66 MHz.

Table 5. Power Supply Characteristics – 2 (Sheet 1 of 2)

| Symbol          | Parameter                          | Condition            | Min                     | Тур | Max                     | Units |

|-----------------|------------------------------------|----------------------|-------------------------|-----|-------------------------|-------|

| V <sub>IH</sub> | Input high voltage                 | LVTTL                | 2.0                     |     | V <sub>DD(3.3)</sub>    | V     |

|                 |                                    | 5 V tolerant         | 2.0                     |     | 5.5                     |       |

|                 |                                    | 3.3 V PCI            | 0.5 <sub>VDD(3.3)</sub> |     | V <sub>DD(3.3)</sub>    |       |

| V <sub>IL</sub> | Input low voltage                  | LVTTL                | VSS                     |     | 0.8                     | V     |

|                 |                                    | 5 V tolerant         | VSS                     |     | 0.8                     |       |

|                 |                                    | 3.3 V PCI            | VSS                     |     | 0.3V <sub>DD(3.3)</sub> |       |

| V <sub>T+</sub> | Switching threshold: Positive edge | LVTTL & 5 V tolerant | 1.2                     |     | 2.4                     | V     |

| V <sub>T+</sub> | Switching threshold: Negative edge | LVTTL & 5 V tolerant | 0.6                     |     | 1.8                     | V     |

| V <sub>H</sub>  | Schmitt trigger-hysteresis         |                      | 0.3                     |     | 1.5                     | V     |

$<sup>\</sup>dot{M}$ aximum conditions are  $T_A$  = minimum, voltages are maximum. Where applicable, network traffic is continuous at full duplex and the system interface is PCI-X 100 to 133 MHz.

In the powerdown mode, the controller is in the D3<sub>hot</sub> state, with PME# wake-up enabled. Link is present at 100 Mbps. In the quiescent mode, the controller is in the D3<sub>cold</sub> state, with wake-up disabled. Link is not present.

Table 5. Power Supply Characteristics – 2 (Sheet 2 of 2) (Continued)

| Symbol           | Pai                             | ameter           | Condition                            | Min                          | Тур | Max  | Units |